# Libero SoC v12.4

# **Release Notes**

05/2020

Microsemi Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

www.microsemi.com

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiationhardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable antitamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Learn more at <u>www.microsemi.com</u>.

51300226-2.0/05.20

# **Revision History**

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# **Revision 2.0**

- Added new section 4.20.1, <u>Installer Appears to Hang or Become Stalled</u>.

- Section 4.12, <u>Design with Relative Paths</u>. Added descriptions for the following know issues:

- o Broken links are shown for locally copied files when project is migrated to a different machine

- Missing components in SmartDesign when project is migrated from Windows to Linux and viceversa

- Components inside SmartDesign are not updated correctly when project is migrated between different machines

- Added <u>Place & Route</u> section to Known Issues.

- Added <u>RT PolarFire CG1509</u> section to Known Issues.

# **Revision 1.0**

Revision 1.0 is the first publication of this document.

# Contents

| Re  | vision | History                            | ۲                                                                     | 3  |  |  |  |

|-----|--------|------------------------------------|-----------------------------------------------------------------------|----|--|--|--|

|     | Revisi | on 2.0                             |                                                                       | 3  |  |  |  |

|     | Revisi | on 1.0                             |                                                                       | 3  |  |  |  |

| Lib | ero So | oC v12.4                           | 4 Software Release Notes                                              | 8  |  |  |  |

|     | 1.1.   | Customer Notification (CN) Support |                                                                       |    |  |  |  |

|     |        | 1.1.1                              | RTG4 SET Filter Delay Calibration Update                              | 8  |  |  |  |

|     |        | 1.1.2                              | RTG4 SERDES and FDDR PLL Enhanced Calibration                         | 8  |  |  |  |

|     |        | 1.1.3                              | Configure I/O States During JTAG Programming Tool                     | 9  |  |  |  |

|     |        | 1.1.4                              | PolarFire FPGA TVS Powerdown                                          | 9  |  |  |  |

|     |        | 1.1.5                              | PolarFire FPGA TVS Temperature Flags                                  | 9  |  |  |  |

|     |        | 1.1.6                              | PolarFire FPGA System Controller and JTAG TRSTB                       |    |  |  |  |

|     |        | 1.1.7                              | PolarFire Netlist Generated for LSRAM Asymmetric Two-port RAMs        |    |  |  |  |

|     |        | 1.1.8                              | PolarFire FPGA PCIE Register Update                                   | 10 |  |  |  |

|     |        | 1.1.9                              | PolarFire Certain Unused IOs were not Tristated when Programmed       | 10 |  |  |  |

|     |        | 1.1.10                             | PolarFire LSRAM CLK-to-OUT Delays                                     | 11 |  |  |  |

|     | 1.2.   | New De                             | vice Support                                                          | 11 |  |  |  |

|     |        | 1.2.1                              | RT PolarFire                                                          | 11 |  |  |  |

|     |        | 1.2.2                              | PolarFire Military Operating Condition                                | 11 |  |  |  |

|     | 1.3.   | Softwar                            | oftware Features and Enhancements                                     |    |  |  |  |

|     |        | 1.3.1                              | Runtime Improvements                                                  | 12 |  |  |  |

|     |        | 1.3.2                              | PolarFire Post Layout Simulation                                      | 12 |  |  |  |

|     |        | 1.3.3                              | Post Layout Clock Domain Crossing (CDC) Report and GUI                | 12 |  |  |  |

|     |        | 1.3.4                              | Timing Reports                                                        | 12 |  |  |  |

|     |        | 1.3.5                              | Minimum Delay Violations Repair Enhancement                           | 12 |  |  |  |

|     |        | 1.3.6                              | Synthesis Enhancements                                                | 13 |  |  |  |

|     |        | 1.3.7                              | Relative Path Enhancement for Linked Files                            | 13 |  |  |  |

|     |        | 1.3.8                              | Multiuser Environment                                                 | 13 |  |  |  |

|     |        | 1.3.9                              | Debug Enhancements                                                    | 13 |  |  |  |

|     |        | 1.3.10                             | Libero Installer Upgrade                                              | 13 |  |  |  |

|     |        | 1.3.11                             | Ubuntu Support                                                        | 14 |  |  |  |

|     |        | 1.3.12                             | 2TB and Greater Partition Size Support                                | 14 |  |  |  |

|     | 1.4.   | New Sili                           | con Features and Enhancements                                         | 14 |  |  |  |

|     |        | 1.4.1                              | PolarFire                                                             | 14 |  |  |  |

|     |        | 1.4.2                              | RTG4                                                                  | 16 |  |  |  |

| 2   | Migr   | ating D                            | esigns to Libero SoC v12.4                                            | 17 |  |  |  |

|     | 2.1    | Design a                           | and Core Invalidation                                                 |    |  |  |  |

|     |        | 2.1.1                              | Programming Files Invalidation                                        | 17 |  |  |  |

|     |        | 2.1.2                              | RTG4 Filter Calibration Design Invalidation and RTG4UPROM Core Update | 17 |  |  |  |

|   |      | 2.1.3    | RTG4 SERDES and Fabric DDR Core Update                                           | 18 |

|---|------|----------|----------------------------------------------------------------------------------|----|

|   |      | 2.1.4    | PolarFire Temperature and Voltage (TVS) Interface Core Invalidation and Update   | 18 |

|   | 2.2  | Core Er  | nhancements and Upgrades                                                         | 18 |

|   | 2.3  | Core U   | pdate Procedure                                                                  | 22 |

| 3 | Reso | lved Is  | sues                                                                             | 23 |

| 4 | Knov | wn Issu  | es and Limitations                                                               | 29 |

|   | 4.1  | Catalog  | g Cores                                                                          | 29 |

|   |      | 4.1.1    | Core Generation Language                                                         | 29 |

|   |      | 4.1.2    | Linux: Core Generation Fails in Batch Mode when the DISPLAY Variable is Not Set  | 29 |

|   |      | 4.1.3    | Core Version Upgrade                                                             | 29 |

|   |      | 4.1.4    | New Cores Are Available Pop-up Message                                           | 29 |

|   |      | 4.1.5    | Core Generation Issues                                                           | 29 |

|   | 4.2  | Project  | Manager Design Hierarchy                                                         | 30 |

|   |      | 4.3.1    | HDL Language Duplicate Modules                                                   | 30 |

|   |      | 4.2.2    | Multiple Definitions Error Message for RTG4FCCC and RTG4FCCCECALIB               | 30 |

|   | 4.3  | Tcl Supp | port Limitations                                                                 | 30 |

|   |      | 4.3.1    | Parameters for SgCore and SystemBuilder Components are not Documented            | 30 |

|   | 4.4  | SmartD   | esign                                                                            | 31 |

|   |      | 4.4.1    | Modify Memory Map Feature Should Not be Used                                     | 31 |

|   |      | 4.4.2    | Export Component Description (Tcl)                                               | 31 |

|   |      | 4.4.3    | Special Characters in Element Names                                              | 31 |

|   | 4.5  | Synthe   | sis                                                                              | 31 |

|   |      | 4.5.1    | SynplifyPro Mapping of Sequential Shift to uSRAM Does Not Support Initial Values | 31 |

|   |      | 4.5.2    | Standalone Synthesis Flow                                                        | 31 |

|   |      | 4.5.3    | SmartFusion2/IGLOO2 with Libero Derived Constraints May Cause Synthesis Warning  | 32 |

|   | 4.6  | I/O Edit | tor                                                                              | 32 |

|   |      | 4.6.1    | DRC Validation                                                                   | 32 |

|   | 4.7  | Netlist  | Viewer                                                                           | 32 |

|   |      | 4.7.1    | Multiple Views                                                                   | 32 |

|   | 4.8  | Place a  | nd Route                                                                         | 32 |

|   |      | 4.8.1    | Place & Route Failure for "get_clocks" in the "-to" Portion of Timing Constraint | 32 |

|   | 4.9  | PolarFi  | re Block Flow                                                                    | 33 |

|   |      | 4.9.1    | Block Components                                                                 | 33 |

|   |      | 4.9.2    | Replication                                                                      | 33 |

|   | 4.10 | PolarFi  | re SSN Analyzer                                                                  | 33 |

|   |      | 4.10.1   | Deviation                                                                        | 33 |

|   | 4.11 | SmartP   | ower                                                                             | 33 |

|   |      | 4.11.1   | Initialize Frequencies & Probabilities with Vectorless Analysis                  | 33 |

|   | 4.12 | Design   | with Relative Paths                                                              | 33 |

|   |      | 4.12.1   | ENVM Serialization Client                                                        | 33 |

|      | 4.12.2           | Broken Links are Shown for Locally Copied Files<br>When Project Migrates to a Different Machine | 34       |

|------|------------------|-------------------------------------------------------------------------------------------------|----------|

|      | 4.12.3           | Components are Missing in SD When Project                                                       |          |

|      |                  | Migrates from Windows to Linux and Vice-Versa                                                   | 34       |

|      | 4.12.4           | Components Inside SD are not Updated Properly                                                   |          |

|      |                  | When Project Migrates between Different Machines                                                |          |

| 4.13 |                  | re Silicon Support Limitations                                                                  |          |

|      | 4.13.1           | Transceivers                                                                                    |          |

|      | 4.13.2           | IOD Interfaces                                                                                  |          |

|      | 4.13.3           | PF_CCC DLL Reference Clock Minimum Frequency                                                    |          |

|      | 4.13.4           | PF_SPI                                                                                          |          |

|      | 4.13.5           | I/O's: SSTL15 On-Die Termination Values Are Programmed Incorrectly                              |          |

| 4.14 | PolarFir         | re Power Estimator                                                                              |          |

|      | 4.14.1           | Design without I/Os                                                                             |          |

| 4.15 | PolarFir         | re Post Layout Simulation                                                                       | 37       |

|      | 4.15.1           | Exception Error Related to Power Nets in Some BA Designs                                        | 37       |

| 4.16 | RT Pola          | rFire Silicon Support Limitations                                                               | 37       |

|      | 4.16.1           | CG1509 Pinout                                                                                   | 37       |

| 4.17 | RTG4 SF          | RAM (AHBLite and AXI)                                                                           | 37       |

|      | 4.17.1           | Initialize RAM for Simulation                                                                   | 37       |

| 4.18 | Identify         | / Debugger                                                                                      | 37       |

|      | 4.18.1           | Identify Instrumentor May Hang on Windows 10 Machines                                           | 37       |

| 4.19 | Aldec S          | imulator                                                                                        | 37       |

|      | 4.19.1           | Simulation Stuck with Aldec Simulators                                                          | 37       |

| 4.20 | Installa         | tion and System Limitations                                                                     |          |

|      | 4.20.1           | Installer Appears to Hang or Become Stalled                                                     |          |

|      | 4.20.2           | FlashPro6 Driver Reinstallation Reports Error Message                                           |          |

|      | 4.20.3           | 4K and 8K screens are Not Supported                                                             |          |

|      | 4.20.4           | Installation on Local Drive Only                                                                |          |

|      | 4.20.5           | Visual C++ Redistributable Installation Error                                                   |          |

|      | 4.20.6           | Installation on Windows 7                                                                       |          |

|      | 4.20.7           | Installation Fails when There is Insufficient Space                                             |          |

|      | 4.20.8           | Linux Package Notes                                                                             |          |

| 4.21 | Antiviru         | us Software Interaction                                                                         |          |

| 4.22 | Program          | nming                                                                                           | 40       |

|      | 4.22.1           | Libero Programming                                                                              | 40       |

|      | 4.22.2           | SPI Flash Programming                                                                           | 41       |

|      | 4.22.3           | sNVM Write Fails Due to ROM Client Created by Previous Design                                   | 41       |

|      |                  | Varify During DDOCDANA Action Fails for Design with Custom User Converts                        |          |

|      | 4.22.4           | Verify During PROGRAM Action Fails for Design with Custom User Security                         | 41       |

|      | 4.22.4<br>4.22.5 | STAPL Programming is Not Supported Using FP6                                                    |          |

|      |                  |                                                                                                 | 41       |

|      | 4.22.5           | STAPL Programming is Not Supported Using FP6                                                    | 41<br>42 |

|   |       | 4.23.1   | Job Manager May Crash During the Import Job Status Operation                      | 42 |

|---|-------|----------|-----------------------------------------------------------------------------------|----|

|   |       | 4.23.2   | Job Manager Crashes When Opening an Existing Job Manager Project from v11.9       | 42 |

|   |       | 4.23.3   | Job Manager Does Not Support PolarFire DAT Export                                 | 42 |

|   |       | 4.23.4   | SmartFusion2/IGLOO2: eNVM Update Protection with FlashLock is No Longer Supported | 42 |

|   |       | 4.23.5   | ERASE Action Failure for FlashPro Express Job                                     | 42 |

|   |       | 4.23.6   | Job Manager init_bitstream Tcl Command Limitation                                 | 43 |

|   | 4.24  | SmartD   | ebug                                                                              | 43 |

|   |       | 4.24.1   | General SmartDebug Limitations                                                    | 43 |

|   |       | 4.24.2   | PolarFire Transceiver Support Limitations                                         | 43 |

|   |       | 4.24.3   | Eye Monitor Limitation on 8b10b PCS-PMA Mode XCVR Lanes                           | 43 |

|   |       | 4.24.4   | SmartBERT Limitations                                                             | 44 |

|   |       | 4.24.5   | Static Pattern Transmit Limitation                                                | 44 |

|   |       | 4.24.6   | Eye Monitor TCL Limitation                                                        | 44 |

|   |       | 4.24.7   | PolarFire FPGA Hardware Breakpoint (FHB) Limitations                              | 44 |

|   |       | 4.24.8   | SmartFusion2/IGLOO2 FPGA Hardware Breakpoint (FHB) Limitations                    | 45 |

|   |       | 4.24.9   | RTG4 FPGA Hardware Breakpoint (FHB) Limitations                                   | 45 |

|   |       | 4.24.10  | RTG4 LSRAM Data Corruption                                                        | 45 |

|   |       | 4.24.11  | Standalone SmartDebug Limitations                                                 | 45 |

|   |       | 4.24.12  | Auto-Chain Construct Limitation in Standalone SmartDebug                          | 46 |

|   |       | 4.24.13  | TCK Frequency Not Reflected in SmartDebug Operations                              | 46 |

|   |       | 4.24.14  | FlashPro6 Programmer Not Detected When Creating a SmartDebug Project              | 46 |

|   |       | 4.24.15  | Incorrect Programmer Information Reported for FlashPro6                           | 46 |

| 5 | Svste | m Real   | uirements                                                                         | 47 |

| 5 | 5,1   |          | ed 64-bit Operating Systems                                                       |    |

|   | 5.2   |          | n-Access Memory (RAM) Requirements                                                |    |

|   | 5.2   | Randoi   |                                                                                   |    |

| 6 | Dow   | nload L  | ibero SoC v12.4 Software                                                          | 48 |

| 7 | Арре  | endix A: | Sample Programming and SmartDebug Times Using FlashPro5/FlashPro6                 | 49 |

| 8 | Appe  | endix B. | RTG4 SPLL and FPLL Calibration and Workaround                                     | 51 |

|   | 8.1   |          | d Designs and Modes                                                               |    |

|   | 8.2   |          | w CoreABC Sequence                                                                |    |

|   | 8.3   |          | Updates for PCIE_SERDES_IF in PCIE Mode                                           |    |

|   | 8.4   | -        | Updates for PCIE_SERDES_IF or NPSS_SERDES_IF in XAUI Mode                         |    |

|   | 8.5   |          | Updates for RTG4FDDRC                                                             |    |

|   | 8.6   | -        | Updates for RTG4FCCCECALIB                                                        |    |

| 9 | Docu  | uments   | Updated in this Release                                                           | 56 |

# Libero SoC v12.4 Software Release Notes

The Libero<sup>®</sup> system on chip (SoC) v12.4 unified design suite is Microchip's flagship FPGA software, for designing with Microsemi's latest power efficient flash <u>FPGAs</u>, <u>SoC FPGAs</u>, and <u>rad-tolerant FPGAs</u>. The suite integrates industry standard Synopsys <u>Synplify Pro</u><sup>®</sup> synthesis and Mentor Graphics <u>ModelSim</u><sup>®</sup> simulation with best-in-class constraints management, debug capabilities, and secure production programming support.

Use Libero SoC v12.4 for designing with Microsemi's <u>RTG4</u> Rad-Tolerant FPGAs, <u>SmartFusion</u><sup>®</sup>2 and <u>IGLOO</u><sup>®</sup> <u>2</u><sup>®</sup> SoC FPGAs, and <u>PolarFire</u> FPGAs.

To design with Microsemi's older Flash FPGA families, use Libero SoC v11.9 and subsequent service packs.

To access datasheets, silicon user guides, tutorials, and application notes, visit <u>www.microsemi.com</u>, navigate to the relevant product family page, and click the **Documentation** tab. <u>Development Kits &</u> <u>Boards</u> are listed in the **Design Resources** tab.

**Note**: Libero SoC v12.4 does not support Classic Constraint Flow. IGLOO2, SmartFusion2 and RTG4 projects using the 'Classic' flow cannot be opened in this release. See <u>Migrating an Existing Project</u> <u>Created with Classic Constraint Flow to Enhanced Constraint Flow</u> for details about how to migrate Classic Constraint Flow projects to the Enhanced Constraint Flow.

# 1.1. Customer Notification (CN) Support

Libero SoC v12.4 includes changes that address certain important issues.

#### 1.1.1 RTG4 SET Filter Delay Calibration Update

RTG4 devices employ Single Event Transient (SET) filters for SET mitigation. These filters are optionally available for flip-flops in Fabric LEs, IOFF, Math blocks, and SRAM blocks via Libero SoC's global SET mitigation setting or the NDC set\_mitigation constraint. SET mitigation is built into the SerDes and FDDR flip-flops. SpaceWire clock and data recovery circuits embedded in the CCCs include a similar, delay-based glitch filter. Libero SoC v12.4 includes an update to ensure SET filters use the intended, Process, Voltage, and Temperature (PVT)-compensated delay values (600ps typical) from the built-in Delay Calibration (DELCAL) circuits located at the SE and NE device corners. Previous versions of Libero allowed SET filters to use an unintended filter delay value. This may result in incorrect ECC operation of LSRAMs in non-pipelined ECC mode with SET mitigation enabled.

While the updated SET delay calibration has been tested extensively, a full validation has not been completed at this time due to mandatory closure of the lab facilities during the COVID-19 pandemic. Validation will be completed as soon as public health conditions permit reopening of lab facilities.

Refer to section 2 for instructions about migrating a design to Libero SoC v12.4. For

more information, refer to PCN20005.

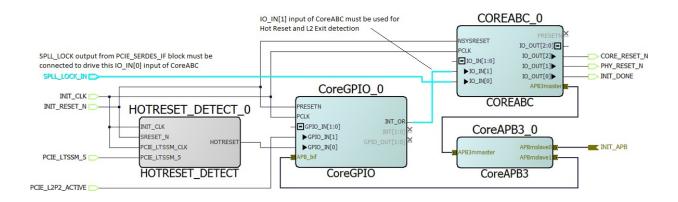

#### 1.1.2 RTG4 SERDES and FDDR PLL Enhanced Calibration

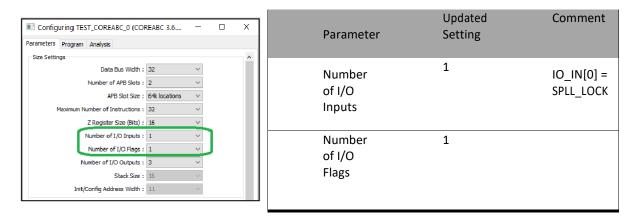

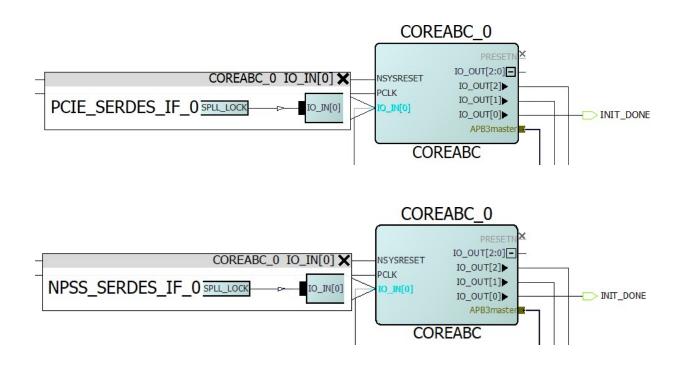

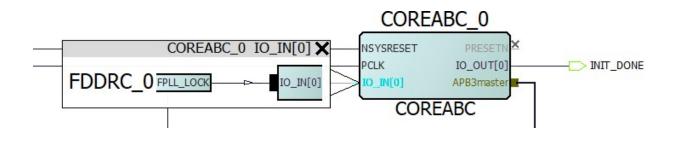

RTG4 PLLs can experience loss of lock at high temperature after being initialized, via device power-up or PLL reset, at cold temperature. Once loss of lock occurs, the PLL lock can be recovered by issuing a reset to the PLL. Libero SoC v12.4 enhances the calibration of the single-thread PLLs in the Fabric DDR controller PLL (FPLL) and for the SerDes PLL (SPLL) in the XAUI and PCI Express physical coding sublayer so that the

VCO is provided with additional gain at reset, and is capable of maintaining lock throughout the entire military temperature operating range. FDDR and SerDes configuration cores will generate enhanced CoreABC initialization microcode that applies the PLL calibration sequence during the subsystem initialization.

There is no core invalidation. Refer to <u>section 2</u> for instructions about migrating a design to Libero SoC v12.4.2 <u>Migrating Designs to Libero SoC v12.4</u>

For more information, refer to <u>CN19009B</u>.

# 1.1.3 Configure I/O States During JTAG Programming Tool

For versions of Libero SoC, v12.0 through v12.3, using the configuration tool to "Configure I/O States During JTAG Programming" can cause a loss of user programming settings selected via "Configure Programming Options", "Configure Action/Procedure" for the "Run Programming Action" step, and "Generate Bitstream" options. This issue applies to all SmartFusion2, IGLOO2, RTG4, and PolarFire devices.

If you used the "Configure I/O States During JTAG Programming" in Libero SoC v12.0 through v12.3, you must update to Libero SoC v12.4. Refer to <u>section 2</u> for instructions about migrating a design to Libero SoC v12.4.<u>2 Migrating Designs to Libero SoC v12.4</u>

For more information, refer to <u>CN20006.1</u> and <u>CN20003.3</u>.

# 1.1.4 PolarFire FPGA TVS Powerdown

The automatic Powerdown of the TVS Sensor between conversions feature of the PolarFire (TVS) Temperature-Voltage Sensor has been found to be ineffective for its intended design purpose. For this reason, it is being deprecated from the TVS module and will no longer be supported in software.

PF\_TVS v1.0.110, which is part of Libero SoC v12.4, addresses this issue. Refer to <u>section 2.1.4</u> for instructions about migrating a design to use this core version.

For more information, refer to <u>CN19029</u>.

# 1.1.5 PolarFire FPGA TVS Temperature Flags

The TRIGGER\_TEMP\_LOW and TEMP\_HIGH flags are not handled properly when the Libero SoC TVS configurator generates the TVS module. As a result, the temperature flags of the PolarFire FPGA Temperature-Voltage Sensor(TVS) trigger at wrong values when set by users in Libero SoC.

PF\_TVS v1.0.110, which is part of Libero SoC v12.4, addresses this issue. Refer to <u>section 2.1.4</u> for instructions about migrating a design to use this core version.

For more information, refer to <u>CN19030</u>.

### 1.1.6 PolarFire FPGA System Controller and JTAG TRSTB

In PolarFire designs created by Libero release prior to v12.4 that enable the System Controller Suspend mode, the system controller may unexpectedly stop and enter suspend mode without completing the proper device initialization. Libero SoC v12.4 implements the change to STAPL file generation, Flash Pro Express, and programming using Flash Pro 4/5/6.

There is no design invalidation. If your design enables the System Controller Suspend mode, update the project to Libero SoC v12.4. for programming or regenerate the STAPL file.

For more information, refer to <u>CN20003.1</u>.

#### 1.1.7 PolarFire Netlist Generated for LSRAM Asymmetric Two-port RAMs

PolarFire designs created by Libero release prior to v12.4 that contain Asymmetric Two-port LSRAM configurations of ratio W32:R2 incorrectly writes bits 18 and 19. Additionally, Asymmetric Two-port LSRAM configurations of ratio W32:R1 incorrectly writes bits 17 through 19. Libero SoC v12.4 corrects the Write-data bits of these configurations.

There is no design invalidation. If your design contains either of these configurations, you must update the project to Libero SoC v12.4. Rerun the Synthesize/Compile tool, configure the P&R Incremental option, and complete the entire flow.

For more information, refer to <u>CN20003.2</u>.

#### 1.1.8 PolarFire FPGA PCIE Register Update

The default values in the PCIe BAR register generated prior to Libero SoC v12.4 were incorrect and could impact the BAR addressing in their PCIE system. Incorrect default register values related to PCIE\_BRIDGE in the <u>PolarFire Register Map</u> documentation has been updated in Libero SoC v12.4 to correctly match silicon.

There is no core invalidation. If your design contains a PCIe component with configured PCIe BAR register using the Libero SoC default values prior to v12.4, update the project to Libero SoC v12.4 and upgrade to PCI Express core v2.0.104.

For more information, refer to <u>CN20003.4</u>.

#### 1.1.9 PolarFire Certain Unused IOs were not Tristated when Programmed

PolarFire programming files generated by Libero release prior to v12.4 could lead certain I/Os to being driven, even if they were not used in the design. Libero SoC v12.4 corrects the attributes of these specific unused I/Os. The impacted pins are listed in the device PPAT tables.

| CCC_NW_PLL0_OUT[0:1] | CCC_NW_PLL1_OUT[0:1] |

|----------------------|----------------------|

| CCC_NE_PLL0_OUT[0:1] | CCC_NE_PLL1_OUT[0:1] |

| CCC_SE_PLL0_OUT[0:1] | CCC_SE_PLL1_OUT[0:1] |

| CCC_SW_PLL0_OUT[0:1] | CCC_SW_PLL1_OUT[0:1] |

There is no design invalidation. If your design didn't use any of the above I/Os, you must update the project to Libero SoC v12.4. Rerun the "Generate FPGA programming data" tool and generate the programming file.

For more information, refer to <u>CN20003.5</u>.

#### 1.1.10 PolarFire LSRAM CLK-to-OUT Delays

During timing characterization over temperature, an adjustment was made to the timing model of the PolarFire LSRAM CLK-to-OUT delays that impacts lower temperatures delays (i.e., industrial and extended):

- For max clock-to-out delays, only Bit 0 is impacted: Internal regression shows that less than 1% of designs are impacted and, when there is an impact on design performance, it is less than 2%.

- For min clock-to-out delays, all bits are impacted: In this case, the delays through the LSRAM are large enough not to show up as min delay critical paths. Internal regression confirmed that no violation was observed due to this change.

There is no design invalidation. Although it is unlikely that this change will have any timing violations on existing designs, we recommend rerunning static timing analysis with SmartTime using Libero SoC v12.4 to ensure your design remains timing violation clear.

For more information, refer to <u>CN20003.6</u>.

### **1.2.** New Device Support

#### 1.2.1 RT PolarFire

Libero SoC v12.4 introduces the Radiation Tolerant **RT PolarFire** device **RTPF500T-CG1509** MIL temp, STD speed-grade. SynplifyPro can infer Soft triple module redundancy (TMR) for inferred FFs. You can use TMR to mitigate SEUs in any part of the design. P&R separates the TMR FFs physically to mitigate clock transients and upsets.

You can start making pin assignments for the new CG1509 Ceramic package. To optimize PCB layout and signal integrity of DDR signals, DDR3 and DDR4 pin assignments will be altered in the next release of Libero SoC. These changes will affect only DDR3 and DDR4 I/Os, and will not affect any other I/O assignment. Place and route performed with Libero SoC v12.4 will be invalidated when Libero SoC v12.5 is invoked. Timing and Power is in "Advance" state. Programming and BSDL export of this device is not yet enabled.

#### 1.2.2 PolarFire Military Operating Condition

Production timing support has been added for the following devices:

- MPF200TS MIL temp, 1.0V, STD speed grade

- MPF500TS MIL temp, 1.0V, STD speed grade

Preliminary timing support has been added for the following devices:

- MPF200TS MIL temp, 1.05V STD speed grade

- MPF300TS MIL temp, 1.05V STD speed grade

- MPF500TS MIL temp, 1.05V STD speed grade

# **1.3.** Software Features and Enhancements

#### **1.3.1** Runtime Improvements

Libero SoC v12.4 includes faster timing report generation (up to 40% compared to v12.3), particularly on large designs with multiple clock domains.

Synthesis runtime of PolarFire designs improve by an average of 25% due to Automatic Compile Points being enabled by default.

#### 1.3.2 PolarFire Post Layout Simulation

Libero SoC v12.4 enables Back-Annotated simulation for fabric components in PolarFire designs.

#### 1.3.3 Post Layout Clock Domain Crossing (CDC) Report and GUI

Libero SoC v12.4 introduces a clock domain crossing report that is generated after P&R. This report identifies potential areas of data loss or meta-stability that can be caused by signals crossing clock domains. To view this report from the SmartTime GUI, select the Tool  $\rightarrow$  Reports  $\rightarrow$  Report CDC menu.

For more details, refer to the <u>SmartTime User Guide</u>.

#### 1.3.4 Timing Reports

Libero SoC v12.4 extends the configurations of Verify Timing for customizing the generated Timing reports in PolarFire designs. The new Report settings:

- Are available in XML, Text, CSV (Tcl only), and HTML (Tcl only) formats.

- Limit the number of reported paths per section.

- Limit the number of expanded paths per section.

- Limit the number of parallel paths per expanded path.

- Maximum slack threshold for Timing Violations report.

In Libero SoC v12.3, we introduced consolidated "multi-corner" timing and violation reports (see section

**1.3.5** of <u>Libero SoC v12.3 release notes</u> for a detailed description). Libero SoC v12.4 removes the frequency information from the Summary section of the consolidated "multi-corner" timing report. This information was an outdated inheritance from the single-corner timing report and was misleading because its value did not account for CDC requirements. This information still appears in the various single-corner reports for compatibility reasons.

#### 1.3.5 Minimum Delay Violations Repair Enhancement

In Libero SoC v12.4, min-delay repair has been enhanced to explore worst-case paths from all corners simultaneously. This results in fewer iterations to close timing for different corners.

#### 1.3.6 Synthesis Enhancements

SynplifyPro 2019.03MSp1-1 included in Libero SoC v12.4 contains the following enhancements:

- Ternary operations inference using a single carry-chain comparator (up to 66)

- PolarFire LSRAM Inference with asymmetric widths

- PolarFire Improved runtime: Automatic compile points enabled by default. SynplifyPro executes multi-threaded when Compile points are enabled. Design iterations resynthesize only the Compile points that were modified, reducing the synthesis time.

For more details, refer to the following documents:

- Synopsys FPGA Synthesis Synplify Pro ME P2019.03MSP1-1 User Guide

- Synopsys FPGA Synthesis Synplify Pro ME P2019.03MSP1-1 Reference Manual

- Synopsys FPGA Synthesis Synplify Pro ME-P2019.03MSP1-1 HDL Language Support Reference Manual

- Synopsys FPGA Synthesis Synplify Pro ME P2019.03MSP1-1 Command Reference Manual

- <u>Synopsys FPGA Synthesis Synplify Pro ME P2019.03MSP1-1 Attribute Reference Manual</u>

- Synopsys<sup>®</sup> FPGA Design Microsemi Edition Release Notes

#### 1.3.7 Relative Path Enhancement for Linked Files

Support for linked files has been enhanced in Libero SoC v12.4 to make it easier to port projects across users and/or machines. Now users can specify an environment variable that defines the base path from which the link file relative path must be calculated. If the environment variable is not specified, the path calculation defaults to legacy behavior.

For more details, refer to the <u>Libero SoC User Guide</u>.

#### 1.3.8 Multiuser Environment

Libero SoC v12.4 provides the ability to lock the core vault location, the synthesis and simulation profiles to the software release. One can create a special profile in the software release installed area to define which vault, synthesis and simulation tools to use for that release. Once defined in that release-level profile, these settings cannot be overridden from Libero. This guaranteed inadvertent changes to the settings for users working with multiple projects and releases of Libero and Libero SoC.

To create an admin profile, invoke adminProfile.exe from the Libero or Designer's /bin location.

For more details, refer to the <u>UG0758</u>: <u>User Guide PolarFire FPGA Design Flow Libero SoC v12.4</u> or the <u>UG0691 User Guide Libero SoC Design Flow Libero SoC v12.4</u> - <u>SmartFusion2</u>, <u>IGLOO2</u>, <u>RTG4</u>.

#### 1.3.9 Debug Enhancements

Identify P2019.03MSp1-1 included in Libero SoC v12.4 supports debugging using FlashPro6.

#### 1.3.10 Libero Installer Upgrade

For ease of use, the Libero SoC v12.4 installer has been enhanced to include an optional Libero license installation flow. The Libero installer now supports three integrated flows:

- Libero tool installation

- Libero license installation

- Integrated tool and license installation

The installer includes a Tcl-based example that runs the Libero-synthesis-simulation flow to check for license issues.

#### 1.3.11 Ubuntu Support

Libero SoC v12.4 introduces support for Ubuntu 18.04. Customers can now install Libero SoC v12.4 on an Ubuntu platform. For details, refer to "<u>System Requirements</u>" on page 47. For installation details, refer to the UG0710 Libero SoC Linux Environment Setup User Guide.

#### 1.3.12 2TB and Greater Partition Size Support

Libero SoC v12.4 now fully supports Linux environments using partitions greater than 2TB, including installing Libero and locating Libero projects.

# 1.4. New Silicon Features and Enhancements

#### 1.4.1 PolarFire

#### **Transceiver Enhancements**

Libero SoC v12.4 enhances the PolarFire Transceiver Enhanced Receiver Management (ERM) Solution to support independent receive and transmit data rates in PMA and PCS-8b10b modes on the same physical lane.

Each PolarFire Transceiver Enhanced Receiver Management (ERM) component has the following options: full duplex, independent receive and transmit, and receive only. These options allow functionality to be assigned efficiently to each lane and help solutions that use small package offerings when transceiver lanes are limited.

Libero SoC v12.4 adds a new option to configure Transmit PLL in integer mode. The Transmit PLL supports Fractional-N and a new integer mode. Fractional-N provides fine grain flexibility for reference clock selection. The new integer mode provides designers with a simplified calculation for direct integer multiples of the reference clock.

Libero SoC v12.4 enhances the Transmit PLL Jitter Attenuation solution significantly when using the Custom Protocol mode. The enhanced solver allows the JA PLL to achieve close to or Oppm with any valid FIN clock frequency. When using the recovered clock from a Transceiver lane as reference clock source (FIN) to the Transmit PLL using 'Fabric routing', the input jitter on JA reference clock will increase due to noise effects from the FPGA fabric routing. If possible, new designs should avoid using Fabric clock source to the JA\_PLL and use the Dedicated clock source instead.

Libero SoC v12.4 SmartDebug for PolarFire simplifies transceiver receiver signal integrity analysis by including an eye mask that specifies the minimum eye opening.

The PolarFire Transceiver Solution supports an expanded set of CTLE settings. Note that these settings are not yet fully validated, and should not be considered Production.

- For A2 Short/Medium in CDR, CDR Auto and DFE modes the following RX\_CTLE options are available:

- o No\_Peak\_+9.22dB

- No\_Peak\_+4.53dB

- No\_Peak\_+1.76dB

- o 5GHz\_+3.14dB

- For A1 Short/Medium in DFE mode the following RX\_CTLE options are available:

- No\_Peak\_+11.10dB

- No\_Peak\_+6.13dB

- No\_Peak\_+3.39dB

- o 6GHz\_+2.73dB

- o 6GHz\_+3.12dB

For details about CTLE settings, refer to <u>AC483: PolarFire FPGA Transceiver Signal Integrity Application</u> <u>Note</u>.

#### **IOD Interfaces Enhancements**

Previous Libero releases limited the number of I/Os per interface to 32. Libero SoC v12.4 removes this limitation and allows up to 128 I/Os per interface.

Libero SoC v12.4 also adds HS\_IO\_CLK to RX/TX\_CLK\_G training for both the receiver and transmit generic IOD interfaces which, combined with HS\_IO\_CLK to DQ training, enables maximum data rate for the IOD interfaces

For more details, refer to the <u>IO User Guide</u>.

#### **CCC Configuration Report**

Libero SoC v12.4 generates a configuration report for the CCC containing the final values of the CCC configuration registers. This report is generated in the "Design and Memory Initialization" Libero stage, in

.xml and .txt formats, and viewable in the report view.

#### PolarFire SRAM (AHBLite and AXI) ECC Support

Libero SoC v12.4 adds ECC support for the PolarFire SRAM (AHBLite and AXI) core. If the SRAM is initialized with data at power-up, the ECC data is also initialized properly after power-up.

#### PolarFire XCVR Sourced Fabric Clocks and Jitter Compensation

The PolarFire XCVR can source three different clocks into the fabric, TX\_CLK, RX\_CLK, and the REFCLK (FAB\_REF\_CLK). These clocks will contain high frequency jitter that is not reported by Libero in the timing report and SmartTime. It is recommended that users add clock uncertainty constraints to these clocks in their design.

The following list is recommended values for clock uncertainty per clock, resource, and speed-grade.

- FAB\_REF\_CLK on Global: 275ps for STD, 200ps for -1

- FAB\_REF\_CLK on Regional: Not supported

- TX\_CLK\_G on Global: 300ps for STD, 225ps for -1

- TX\_CLK\_R on Regional: 225ps for STD, 150ps for -1

- RX\_CLK\_G on Global: 325ps for STD, 250ps for -1

- RX\_CLK\_R on Regional: 250ps for STD, 175ps for -1

Below is an example clock uncertainty constraint. This constraint would be added to the user's timing SDC file.

# TX\_CLK and RX\_CLK on Regionals

set\_clock\_uncertainty -setup 0.150 [ get\_pins { PF\_XCVR\_ERM\_LANE2/I\_XCVR/LANE0/TX\_CLK\_R } ]

set\_clock\_uncertainty -setup 0.175 [ get\_pins { PF\_XCVR\_ERM\_LANE2/I\_XCVR/LANE0/RX\_CLK\_R } ] # TX\_CLK and

RX\_CLK on Globals

set\_clock\_uncertainty -setup 0.300 [ get\_pins { PF\_XCVR\_ERM\_LANE2/I\_XCVR/LANE0/TX\_CLK\_G } ]

set\_clock\_uncertainty -setup 0.325 [ get\_pins { PF\_XCVR\_ERM\_LANE2/I\_XCVR/LANE0/RX\_CLK\_G } ] # FAB\_REF\_CLK

on Global

set\_clock\_uncertainty -setup 0.275 [get\_clocks PF\_DDR4\_C0\_0/CCC\_0/pll\_inst\_0/OUT1]

A future release of Libero will add these constraints automatically to the derived constraints from the Constraints Manager.

#### 1.4.2 RTG4

#### **RTG4 SRAM (AHBLite and AXI) ECC Support**

Libero SoC v12.4 adds ECC support for the RTG4 SRAM (AHBLite and AXI) core. The option to Initialize RAM for simulation when ECC is enabled will be added in a future release.

# 2 Migrating Designs to Libero SoC v12.4

# 2.1 Design and Core Invalidation

#### 2.1.1 Programming Files Invalidation

As a result of <u>CN20006.1</u> and <u>CN20003.3</u>, Libero SoC v12.4, for all families, will automatically update the affected programming settings and invalidate bitstream generation tools accordingly. The impacted tools are "Configure Programming Options", "Configure Action/Procedure" for the "Run Programming Action" step, and "Generate Bitstream Options".

Rerun any of the affected tools as needed, and reprogram device with updated bitstream.

#### 2.1.2 RTG4 Filter Calibration Design Invalidation and RTG4UPROM Core Update

As a result of <u>PCN20005</u>, all RTG4 designs with completed programming file are invalidated upon migrating a project created in a Libero release prior to v12.4 to Libero SoC v12.4. Completed designs that do not use the uPROM will not require re-running Place & Route, unless that step is invalidated due to other required updates, per the Libero SoC log window.

In the uPROM, total number of available 36-bit words has been reduced from 10,400 to 10,370. This allows space to be reserved for the instructions required to calibrate the filter delay.

New designs are not affected by this upgrade because they will use the updated RTG4UPROM core.

However, completed designs containing uPROM instance require a uPROM core version upgrade and revert to a pre-synthesis/pre-compile state.

Existing designs are impacted as described below:

- If the design does not contain a uPROM component, Libero SoC v12.4 will not invalidate Place and Route, but will invalidate "Generate FPGA Array Data", "Generate Bitstream", "Export Bitstream", and "Export FlashPro Express Job". The impacted flows must be rerun.

- If the design contains a uPROM component, Libero SoC v12.4 will invalidate "Synthesize" / "Compile":

- a. See <u>section 2.3</u> for information about how to update a core. Upgrade the uPROM component to v2.1.100 and rerun the entire flow. The run will fail if the clients exceed 10,370 words.

- b. For a netlist-only project, regenerate the uPROM and rerun synthesis outside Libero.

Rerun the tool flow, including "Generate FPGA Array Data" and "Generate Bitstream" steps. Reprogram device with updated bitstream.

### 2.1.3 RTG4 SERDES and Fabric DDR Core Update

As a result of <u>CN19009B</u>, the enhanced PLL calibration cores for FDDR PLLs and SerDes PLLs are included in the Libero SoC v12.4 software release and must be integrated into existing designs for the enhanced calibration to be applied to FDDR PLL and SerDes SPLL. With this update, all single-thread RTG4 PLLs will have lock stability independent of junction temperature rise during operation within datasheet limits.

See section 8.0 (Appendix B) for details on the enhanced PLL solution for FDDR and SerDes PLL.

See <u>section 2.3</u> for information about how to update a core.

#### 2.1.4 PolarFire Temperature and Voltage (TVS) Interface Core Invalidation and Update

The PolarFire Temperature and Voltage (TVS) Interface core has been updated in Libero SoC v12.4 to account for the changes described in <u>CN19029</u> and <u>CN19030</u>. If a design contains the TVS core, and:

- Temperature sensing channel is enabled: Libero SoC v12.4 will invalidate "Synthesize". The TVS core must be upgraded to the latest version and the full flow must be rerun.

- Temperature sensing channel is not enabled. Libero SoC v12.4 will not invalidate "Synthesize".

See <u>section 2.3</u> for information about how to update a core.

# 2.2 Core Enhancements and Upgrades

If a project created in a Libero release prior to v12.4 contains the following cores, and the cores have been generated, they do not need to be upgraded after migrating the project to Libero SoC v12.4. However, if the core needs to be generated again for any reason (for example, a change in parameters), the latest version from the Catalog must be downloaded and used.

Libero SoC v12.4 includes the following PolarFire core updates from Libero SoC v12.3.

| Display Name                  | Version | Change Description                                                                                                                                                                                                    |

|-------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PolarFire DDR3                | 2.4.111 | There are no functional changes for this version. This new version uses the latest training and IOD sub-core versions.                                                                                                |

| PolarFire DDR4                | 2.4.111 | There are no functional changes for this version. This new version uses the latest training and IOD sub-core versions.                                                                                                |

| PolarFire LPDDR3              | 2.3.111 | There are no functional changes for this version. This new version uses<br>the latest training and IOD sub-core versions. The latest training sub-<br>core version fixes the fast simulation mode for low data rates. |

| PolarFire QDR                 | 1.7.100 | There are no functional changes for this version. The unused QVALID port has been removed from the core.                                                                                                              |

| Transceiver Interface         | 3.0.102 | The transceiver interface core now supports the 'Enhanced Receiver<br>Management' option for the 'Tx and Rx (Independent)' mode.                                                                                      |

| PCI Express                   | 2.0.104 | Some default register values have been updated to match the actual hardware values. See <u>section 1.1.8</u> for more information.                                                                                    |

| Transmit PLL                  | 2.0.202 | The Transmit PLL has been enhanced to improve the Jitter Attenuation (JA) integer solution. It also improves the custom solution to achieve close to or 0ppm resolution.                                              |

| PolarFire IOD CDR<br>Clocking | 2.1.104 | This core has been enhanced to display the TX_CLK_G clock frequency.                                                                                                                                                  |

| Display Name                                             | Version | Change Description                                                                                                                                                                                                    |

|----------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PolarFire IOD Generic<br>Receive Interfaces              | 2.0.123 | The IOD Generic Receive Interfaces core offers multiple enhancements:                                                                                                                                                 |

|                                                          |         | Up to 128 I/Os per interface (from 32 in previous version).                                                                                                                                                           |

|                                                          |         | HS_IO_CLK to RX/TX_CLK_G training, which combined with HS_IO_CLK to DQ training enables maximum data rate for the IOD interfaces.                                                                                     |

| PolarFire IOD Generic<br>Transmit Interfaces             | 2.0.108 | The IOD Generic Transmit Interfaces core offers multiple enhancements:                                                                                                                                                |

|                                                          |         | Up to 128 I/Os per interface (from 32 in previous version)                                                                                                                                                            |

|                                                          |         | HS_IO_CLK to RX/TX_CLK_G training, which combined with HS_IO_CLK to DQ training enables maximum data rate for the IOD interfaces.                                                                                     |

|                                                          |         | Specialized clock port to be connected to the new PolarFire IOD<br>Generic Transmit Interfaces Clocking core required to complete the<br>HS_IO_CLK to RX/TX_CLK_G training solution.                                  |

| PolarFire IOD Generic<br>Transmit Interfaces<br>Clocking | 1.0.121 | The PolarFire IOD Generic Transmit Interfaces Clocking is a new core<br>that is needed as part of implementing the HS_IO_CLK to<br>RX/TX_CLK_G training solution for the PolarFire IOD Generic Transmit<br>Interface. |

| PolarFire RGMII to GMII                                  | 1.2.111 | There are no functional changes for this version. This new version uses the latest IOD sub-core version.                                                                                                              |

| PolarFire SRAM (AHBLite and AXI)                         | 1.2.105 | The new version of this core supports ECC                                                                                                                                                                             |

| PolarFire Dynamic<br>Reconfiguration Interface           | 1.0.102 | There are no functional changes for this version. This new version has an updated User Guide reference.                                                                                                               |

| PolarFire Initialization<br>Monitor                      | 2.0.105 | The CALIB_START port which was added in Libero SoC v12.3 has been removed in this release. The CALIB_START port is automatically removed when upgrading to this new version.                                          |

| Temperature and Voltage<br>Sensor Interface              | 1.0.110 | This version removes the deprecated POWERDOWN option. It also fixes the computation of the temperature thresholds. See <u>section 1.1.4</u> and <u>section 1.1.5</u> for more information.                            |

| CoreSmartBERT                                            | 2.6.101 | There are no functional changes for this version. This new version uses the latest transceiver core version.                                                                                                          |

Libero SoC v12.4 includes the following **RTG4** core updates from Libero SoC v12.3.

| Display Name                                                                   | Version | Changes Description                                                                                                                                                                                              |

|--------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTG4 SRAM (AHBLite and AXI)                                                    | 1.0.110 | The new version of this core supports ECC                                                                                                                                                                        |

| RTG4 uPROM                                                                     | 2.1.100 | Makes room for SET delay re-calibration.<br>All RTG4 designs with RTG4UPROM are invalidated to pre-<br>synthesis/compile state. Users MUST upgrade to 2.1.100.<br>See <u>section 1.1.1</u> for more information. |

| RTG4 DDR Memory<br>Controller                                                  | 2.0.100 | This core version generates a new CoreABC initialization sequence that implements the FDDR FPLL temperature drift calibration solution. See <u>section 1.1.2</u> for more information.                           |

| RTG4 DDR Memory<br>Controller with<br>Initialization                           | 2.0.100 | This core version generates a new CoreABC initialization sequence that implements the FDDR FPLL temperature drift calibration solution. See section 1.1.2 for more information.                                  |

| RTG4 High Speed Serial<br>Interface (PCIe, EPCS &<br>XAUI)                     | 2.0.100 | This core version generates a new CoreABC initialization sequence that implements the Transceiver SPLL temperature drift calibration solution. See <u>section 1.1.2</u> for more information.                    |

| RTG4 High Speed Serial<br>Interface 1 – EPCS and<br>XAUI – with Initialization | 2.0.100 | This core version generates a new CoreABC initialization sequence that implements the Transceiver SPLL temperature drift calibration solution. See <u>section 1.1.2</u> for more information.                    |

| RTG4 High Speed Serial<br>Interface (EPCS & XAUI)                              | 2.0.100 | This core version generates a new CoreABC initialization sequence that implements the Transceiver SPLL temperature drift calibration solution. See <u>section 1.1.2</u> for more information.                    |

| RTG4 High Speed Serial<br>Interface 2 – EPCS and<br>XAUI – with Initialization | 2.0.100 | This core version generates a new CoreABC initialization sequence that implements the Transceiver SPLL temperature drift calibration solution. See <u>section 1.1.2</u> for more information.                    |

See <u>section 2.3</u> for information about how to update a core.

# 2.3 Core Update Procedure

Perform the following procedure to update a core version:

- Download the latest version of the core into your vault.

- Upgrade each configured core in your design to the latest version by right-clicking on the core component in the design hierarchy and selecting **Replace Component Version**.

- Regenerate the design.

- Derive the Timing Constraints again from the Constraint Manager tool to use the latest generated core constraints.

- Rerun the tool flow.

# **3** Resolved Issues

The following table lists the customer-reported defects and enhancement requests resolved in Libero SoC v12.4. Resolution of previously reported "Known Issues and Limitations" are also noted in this table.

| Case Number                            | Description                                                                                                                                                                                                              |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 493642-2701742107                      | Change in timing values after running Verify Timing in v12.3.                                                                                                                                                            |

| 493642-2625748880                      | Clock latency value for IO-Reg[External Hold analysis] paths.                                                                                                                                                            |

| 493642-2689492312                      | In SmartTime, right-clicking on a timing path or expanded timing path does not highlight the net in ChipPlanner.                                                                                                         |

| c493642-2673418401                     | Cross probing unstable with zoom in feature                                                                                                                                                                              |

| 493642-2706645305                      | IO reg combining not working in Netlist flow<br>Resolution:<br>Libero SoC v12.4 fixes an issue with the organization of Netlist<br>Design Constraint (NDC) files for the EDIF/VM post-synthesis netlist<br>flow.         |

| 493642-2718476813<br>493642-2718624799 | Libero v12.3 doesn't honor NDC file for EDIF/VM flow<br>Resolution:<br>Libero SoC v12.4 fixes an issue with the organization of Netlist<br>Design Constraint (NDC) files for the EDIF/VM post-synthesis netlist<br>flow. |

| 493642-2629904414                      | POWERDOWN checkbox in PolarFire TVS IP configurator must be<br>removed<br>Resolution:<br>The Temperature and Voltage Sensor (TVS) Interface core version<br>1.0.110 fixes this issue.                                    |

| 493642-2676058215                      | PF_TVS: temp_low & temp_high flags not correctly working<br>Resolution:<br>The Temperature and Voltage Sensor (TVS) Interface core version<br>1.0.110 fixes this issue.                                                  |

| 493642-2672542990                      | PF_QDR: QDR_PF illegal pad issue in Libero 12.2<br>Resolution:<br>The PolarFire QDR core version 1.7.100 fixes this issue.                                                                                               |

| Case Number       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 493642-2638786872 | PF_SRAM_AHBL_AXI: Enhancement request for EDAC<br>Resolution:<br>The PolarFire SRAM (AHBLite and AXI) core version 1.2.105                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 493642-2671317816 | <ul> <li>implements this enhancement.</li> <li>G4_DDR: For igloo2 DDR2 type and PHY width of 8, burst length of 4 is not supported.<br/>Resolution:</li> <li>Burst Length 8 (BL8) is supported DDR3, DD2 and LPDDR and all data widths.</li> <li>Burst Length 4 (BL4) is supported only for DDR2 and LPDDR and only for data width of 32.</li> <li>Burst Length 16 (BL16) is supported only for LPDDR and only for data width of 16.</li> <li>Design Rule have been added for non-supported configurations</li> <li>Enhancement request - Add AXI4 streaming BIF.</li> </ul> |

| 493642-2677814246 | Resolution:<br>The AXI4 Bus Interface (BIF) has been added to Libero SoC v12.4 and<br>can be used when creating a core from an HDL module.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 493642-2709015110 | PF: Export IBIS deletes the P&R flow in VM netlist design.<br>Resolutions:<br>This defect has been resolved in Libero SoC v12.4.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 493642-2625770311 | Enhancement Request: TCL command to report timing closure<br>pass/fail based on the results of Verify Timing command.<br>Resolution:<br>The following messages are displayed in the log window at the end<br>of the Verify Timing command:<br>If timing violations:<br>Error: Timing constraints have not been met.<br>If no timing violations:<br>Info: Timing constraints have been met.<br>If no timing constraints were set:<br>Warning: No Timing constraints are set.                                                                                                  |

| Case Number                                                                                           | Description                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 493642-1986842740<br>493642-2326709729<br>493642-2531788673<br>493642-2552248549                      | RELATIVE_PATH: Libero SoC prj file has the absolute path for linked<br>HDL<br>Resolution:<br>See the <u>Relative Path Enhancement for Linked Files</u> section for<br>details about this new feature.                                      |

| 493642-2711545965                                                                                     | Inconsistency in exporting stp for MPF devices in Libero v12.3<br>Resolution:<br>When running the export_bitstream_file command, all file formats<br>specified by the -format option are properly as expected.                             |

| 493642-2690544739<br>493642-2728908419                                                                | STP and .dat files not getting exported using exported tcl in Libero<br>12.3<br>Resolution:<br>When running the export_bitstream_file command, all file formats<br>specified by the -format option are properly as expected.               |

| 493642-2436656358<br>493642-2432126472<br>493642-2523772273<br>493642-2609521421<br>493642-2615450581 | Relative paths support in Libero<br>Resolution:<br>See the <u>Relative Path Enhancement for Linked Files</u> section for<br>details about this new feature.                                                                                |

| 493642-2544111080                                                                                     | FP6: Add EXTEST2 instruction to CM3 code to solve I/O glitch issue.                                                                                                                                                                        |

| 493642-2695957773<br>493642-2727763417                                                                | PF_SOC: Issues Power Breakdown by voltage rails/Resource in "MSS & MDDR" sheet                                                                                                                                                             |

| 493642-2722049359                                                                                     | P&R crash without any message<br>Resolution:<br>This defect has been fixed in Libero SoC v12.4.                                                                                                                                            |

| 493642-2725028410                                                                                     | G5layout.exe crash in Libero SoC 12.3<br>Resolution:<br>This defect has been fixed in Libero SoC v12.4                                                                                                                                     |

| 493642-2651035974                                                                                     | Enhancement request for VERIFY TIMING when running multi-pass<br>P&R<br>Resolution:<br>When multi-pass P&R is run, Verify Timing is now properly cleaned-<br>up. To obtain the timing reports, explicitly call Verify Timing after<br>P&R. |

| Case Number                                                   | Description                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 493642-2698404809                                             | RTG4: Add check for valid combination of ulock bits at bitstream gen level.                                                                                                                                                                                                                                         |

| 493642-2643973119                                             | Enhancement request: Save for list of signals in Live Probe.                                                                                                                                                                                                                                                        |

| 493642-2615986097                                             | RTG4 LVDS Output IBIS Models (software export).                                                                                                                                                                                                                                                                     |

| 493642-2678703755,<br>493642-2705388493,<br>493642-2707071569 | VHDL Simulation issue in Modelsim ME (standard version), which was released with Libero SoC v12.2.                                                                                                                                                                                                                  |

| 493642-2596989658                                             | Static ODT "OFF" should not allow to set ODT impedance value                                                                                                                                                                                                                                                        |

| 493642-2664199123                                             | RTG4 design fails min timing on slow corner.<br>Resolution:<br>Repair min-delay violations analyzes paths from all corners starting<br>with Libero SoC v12.4.                                                                                                                                                       |

| 493642-2700092229                                             | new_project tcl command has confusing error message.<br>Resolution:<br>When specifying the family name in the new_project Tcl command,<br>make sure to enter the proper case (e.g., SmartFusion2 and not<br>SMARTFUSION2). The error message has been fixed to show the list<br>of valid families with proper case. |

| 493642-2695913352                                             | TCL command to identify Libero version<br>Resolution:<br>You can use 'libero –version (-release)' on the command line to get<br>the Libero SoC version (release) value.<br>You can use Libero SoC Tcl command get_libero_version<br>(get_libero_release) to get the Libero SoC version (release) value.             |

| 493642-2644630854                                             | project_archive TCL command missing<br>Resolution:<br>The project_archive Tcl command has been added to the Libero SoC<br>v12.4 TCL command reference guide.                                                                                                                                                        |

| 493642-2689522793                                             | PF_UPROM: TCL: Issue adding the clients to the PF_UPROM core through create_and_configure_core TCL command.                                                                                                                                                                                                         |

| Case Number                            | Description                                                                                                                     |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                        | PF_DRI is not documented                                                                                                        |  |  |  |

| 493642-2635269681                      | Resolution:                                                                                                                     |  |  |  |

|                                        | The PolarFire Dynamic Reconfiguration Interface core version 1.0.102 has a proper reference to the User Guide for this feature. |  |  |  |

| 493642-2689492312                      | Not pointing the nets path in Netlist Viewer- Flat Post-Compile                                                                 |  |  |  |